通过氧气等离子体处理的超低导通电压(0.37V)垂直GaN-on-GaN肖特基势垒二极管

2024/6/17 16:34:40 材料来源:ACT化合物半导体

作者:吴钧烨1,廖泽亮1,王灏帆1,邹平1,蔡伟雄1,陈少军1,熊信伯1,黎晓华1,屠宇迪1,刘新科1*,朱仁强2,庄文荣3,邱显钦4;

1深圳大学;2成都电子科技大学深圳高等研究院;3东莞中镓半导体科技有限公司;4长庚大学;

*通信作者xkliu@szu.edu.cn

摘要:在这项研究中,展示了具有超低导通电压VON (0.37 V)的垂直氮化镓(GaN)肖特基势垒二极管(SBD)。由于O2等离子体处理(OPT)工艺,在GaN表面形成了GaON,进一步改变了材料表面的表面电位,使VON从0.62 V降低到0.37 V。旋涂玻璃(SOG)沉积在器件顶部,形成浮动保护环(FGR),用于通过减少电场分布将击穿电压提高到681 V(J = 1 A/cm2)。垂直GaN SBDs的比导通电阻(RON)为2.6 mΩ·cm2。器件在不同应力时间变化下的劣化表现出轻微的器件稳定性。

关键词:GaN-on-GaN,O2等离子体处理,超低开启电压

由于GaN材料具有优异的物理特性,如宽的带隙(Eg = 3.4 eV)、高电子迁移率和高热导率,氮化镓(GaN)基器件被认为是最有前途的电力电子元件之一。[1-5]研究最广泛的GaN基功率二极管主要分为横向和垂直结构。基于二维电子气(2DEG)通道的横向二极管具有高电子浓度(~1×1013 cm2)和电子迁移率(~2000 cm2/V·s)。[4]然而,横向二极管的性能受到表面相关问题和散热不良的限制。与横向GaN器件相比,垂直GaN器件具有更高的击穿电压、更大的电流和更低的热阻,因为GaN-on-GaN同质外延层具有更好的晶体质量,例如低穿透位错密度(TDD)(~104- 106 cm-2)和界面应力。[6-8]垂直GaN肖特基势垒二极管(SBD)由于其低导通电压和快速反向恢复能力,在功率开关应用中具有明显的优势。[9]SBD的导通电压直接影响器件的功率转换效率和功率损耗,正向压降越低可以带来更低的功耗和更高的开关频率。[10]但是,与Si SBD相比,垂直GaN SBD具有更高的开启电压(VON)(通常> 0.6 V),这意味着该器件在电源系统中具有更大的功率损耗和更低的整流效率。[11]

为了解决这些问题,在之前的研究中,降低导通电压的方法通常是通过更换肖特基接触金属,Chen等人以Mo为阳极制备了开启电压为0.34 V、击穿电压(VBR)为125 V的GaN SBD。[12]在横向GaN SBD中,通常将欧姆阳极和肖特基阳极结合在一起[13-14]以获得较低的开启电压。但导通电压的降低通常会导致器件漏电流的增加,从而降低器件的击穿电压。[15]O2等离子体处理(OPT)也用于修改横向GaN基高电子迁移率晶体管(HEMT)和肖特基二极管的界面和表面态来提高这些器件的性能。[16-18]必须降低导通电压,同时通过场板和沟槽结构等边缘终端确保一定的击穿电压。[19-21]浮动保护环(FGR)是一种有效且易于实施的降低阳极边缘电场的端接方法。[22-24]

在本工作中,通过OPT制备了超低导通电压垂直GaN SBD。将旋涂玻璃(SOG)沉积在器件顶部以形成FGR。经过OPT处理后,VON从0.62 V降至0.37 V。通过OPT工艺和制备终止,垂直GaN SBD表现出超低的开启电压VON为0.37 V,VBR为681 V(在J = 1 A/cm2),比导通电阻(RON)为2.6 mΩ · cm2。使用随温度变化的电流密度-电压(J-V)特性和脉冲应力测试来分析器件的可靠性。

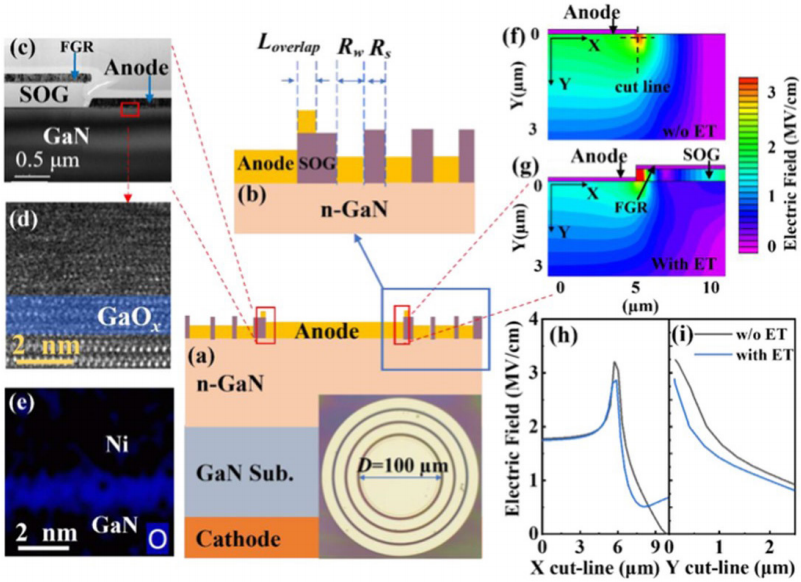

△ 图1:(a)整个横截面示意图,插图显示了带有浮动保护环(FGR)的垂直GaN SBD的顶视图,插图显示了其光学图像。(b)从(a)切下的右侧。(c)阳极/GaN/SOG界面的TEM图像。(d)阳极/GaN界面的TEM图像。(e)阳极/GaN界面处的O元素映射。(f)和(g)分别为不带FGR终端和带FGR终端的垂直GaN SBD的模拟电场分布(f)。分别从(f)和(g)中沿X切割线提取(h)、沿Y切割线提取(i)阳极边缘处的模拟电场分布。

△ 图1:(a)整个横截面示意图,插图显示了带有浮动保护环(FGR)的垂直GaN SBD的顶视图,插图显示了其光学图像。(b)从(a)切下的右侧。(c)阳极/GaN/SOG界面的TEM图像。(d)阳极/GaN界面的TEM图像。(e)阳极/GaN界面处的O元素映射。(f)和(g)分别为不带FGR终端和带FGR终端的垂直GaN SBD的模拟电场分布(f)。分别从(f)和(g)中沿X切割线提取(h)、沿Y切割线提取(i)阳极边缘处的模拟电场分布。

图1(a)显示了具有FGR的垂直GaN SBD结构。它由硅掺杂的300 μm厚的GaN衬底和轻度掺杂的20 μm厚的漂移层组成,掺杂浓度为1×1016cm-3(SINO Nitride, China)。端接结构的细节如图1(b)所示,它是图1(a)的右侧剖视图。首先,晶圆经过预清洗过程,包括5分钟的丙酮、5分钟的异丙醇脱脂步骤和10分钟的强氧化性溶液(H2O2:H2SO4=1:3)浸泡步骤以去除有机残留物。采用BCl3/Cl2等离子刻蚀形成深度为1.2 μm、直径为350 μm的台面结构。使用均胶机制造的SOG来形成FGR。之后,通过(BOE,NH4F:H2O=1:6)进行湿法蚀刻,用于蚀刻SOG。

此后,通过沉积Ti/Al/Ni/Au(25 nm/100 nm/25 nm/40 nm)并在N2环境中在800°C下快速热退火(RTA)30秒来形成欧姆接触。在沉积阳极之前,对GaN表面进行OPT,压力为50毫托,O2流量为30 sccm,等离子体功率为250 W,持续100秒。最后,沉积Ni/Au(25/60 nm)接触作为直径为100 μm的阳极电极和浮动金属环。图1(c)显示了器件阳极/GaN/SOG界面的透射电子显微镜(TEM)图像。图1(d)和(e)通过能量色散光谱仪(EDS)显示了GaON的存在。

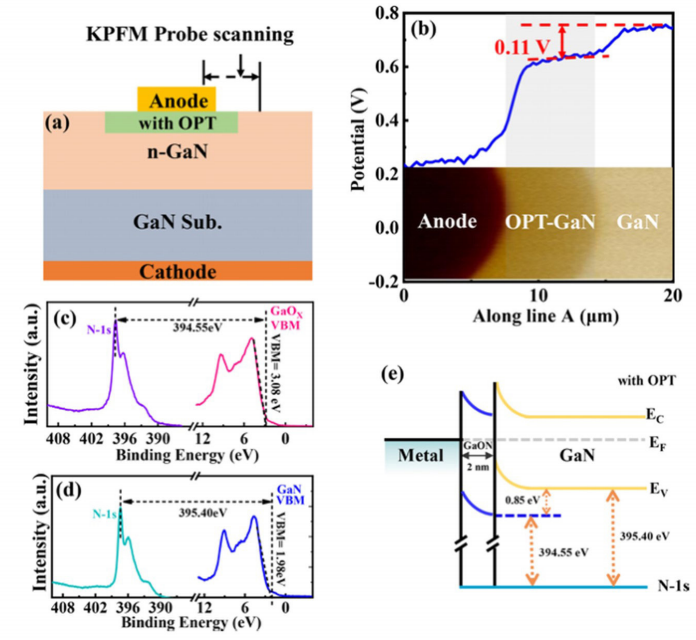

△ 图2:(a)分别是采用OPT进行KPFM测量的样品结构。(b)KPFM对两种类型样品的电位差。分别具有OPT和(d)的样品(c)和(d)的XPS光谱。(e)分别具有OPT的样品的能带图。

△ 图2:(a)分别是采用OPT进行KPFM测量的样品结构。(b)KPFM对两种类型样品的电位差。分别具有OPT和(d)的样品(c)和(d)的XPS光谱。(e)分别具有OPT的样品的能带图。

图1(f)和(g)分别显示了没有和有FGR的垂直GaN SBD的模拟电场分布。比较两种器件之间的电场分布,浮动保护环可以降低肖特基接触边缘的峰值电场,如图1(h)和(i)所示。图2(a)显示了用于开尔文探针力显微镜(KPFM)测量的没有和有OPT的样品结构。KPFM的结果如图2(b)所示,OPT[18]后表面电位降低,这表明GaON和金属的功函数差异小于GaN和金属的差异。从X射线光电子能谱(XPS)中提取的结果,图2(c)和(d)显示了N-1s核能级和价带最大值(VBM)的值,可以通过差值估计GaN和GaON之间的VBM偏移GaN和GaON的N-1s和VBM之间的差异。VBM偏移为0.85eV,GaON纳米层的VBM低于GaN衬底的VBM。GaON的带隙约为4.12–4.22 eV,[25]GaON的导带最小值(CBM)据估计比GaN低0.05-0.15 eV。由于GaON与金属的功函数差异较小,GaON的CBM较低,OPT后肖特基势垒高度(SBH)降低,导致导通电压降低,漏电流增加。图2(e)分别显示了具有OPT的器件的能带图。

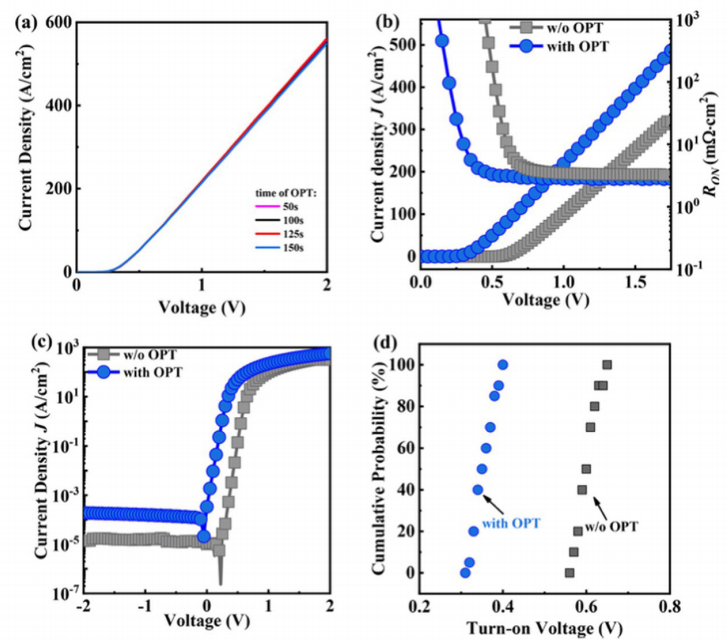

△ 图3:(a)一系列OPT处理时间从50s到150s的正向J-V特性,步长为25s。(b)分别具有和不具有OPT的垂直GaN SBD的正向J-V特性。(c)两种器件的对数标度图中的正向J-V特性。(d)分别有和没有OPT的垂直GaN SBD的VON累积概率。

△ 图3:(a)一系列OPT处理时间从50s到150s的正向J-V特性,步长为25s。(b)分别具有和不具有OPT的垂直GaN SBD的正向J-V特性。(c)两种器件的对数标度图中的正向J-V特性。(d)分别有和没有OPT的垂直GaN SBD的VON累积概率。

一系列OPT处理时间为50 s至150 s的样品的正向J-V特性如图3(a)所示。随着OPT处理时间的增加,开通电压和电流密度变化不大,这是由于OPT时间大于50 s时GaON生长过饱和造成的。如图3(b)所示,带有OPT的器件显示VON为~0.37 V,这是在室温下标准电流密度为1 A/cm2时推断的。在没有OPT的器件中,VON约为0.62 V。通过正向J-V提取的带和不带OPT的器件的SBHΦB,F分别为0.57 eV和0.81 eV。[21]带OPT的器件的RON为2.6 mΩ·cm2,与不带OPT的器件RON相当。2.8mΩ · cm2。图3(c)显示了两种器件的对数标度图中的前向J-V特性。图3(d)显示了带和不带OPT的器件的VON的周期累积概率分布,带和不带OPT过程的每个器件测试了20个器件,概率值每个点是VON出现在这个起点(0%点)和这个点之间的循环中的概率。有OPT的器件的VON在0.3-0.4 V的范围内,而没有OPT的器件的VON在0.55-0.7 V的范围内,表明OPT过程后VON明显下降。

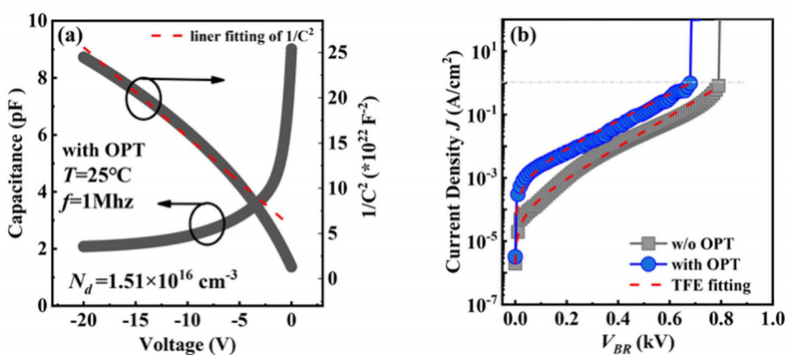

△ 图4:(a)采用OPT的垂直GaN SBD的详细C-V和1/C2-V图。(b)分别有和没有OPT的垂直GaN二极管的反向J-V特性。

△ 图4:(a)采用OPT的垂直GaN SBD的详细C-V和1/C2-V图。(b)分别有和没有OPT的垂直GaN二极管的反向J-V特性。

图4(a)显示了1 MHz下的电容 - 电压(C-V)测量值、净掺杂浓度以及通过1/C2-V图的斜率和交点提取的SBH。净掺杂浓度ND为~1.51×1016 cm-3,SBHΦB,C-V为0.60 eV[26]。由于像力等其他影响,ΦB,C-V比正向J-V估计的要大。

图4(b)分别显示了有和没有OPT的垂直GaN SBD的反向J-V特性。基于热发射(TE)模型的反向J-V提取的ΦB,R为0.58eV,与正向J-V和C-V提取的结果吻合。没有OPT的器件的击穿电压为800V(J=1A/cm2),而有OPT的器件的VBR仍保持在681V的水平,这是由于漏电流的增加造成的。反向漏电流主要是电子从金属侧克服接触界面势垒并通过TE注入半导体而形成。使用热电子场发射(TFE)模型代替TE来分析反向漏电流。[28]如图4(b)所示,带有OPT的垂直GaN SBD的反向J-V特性与TFE模型匹配。高净掺杂浓度ND~1.51×1016 cm-3导致反向漏电流迅速增加。有和没有OPT的器件的漏电流都遵循TFE模型。

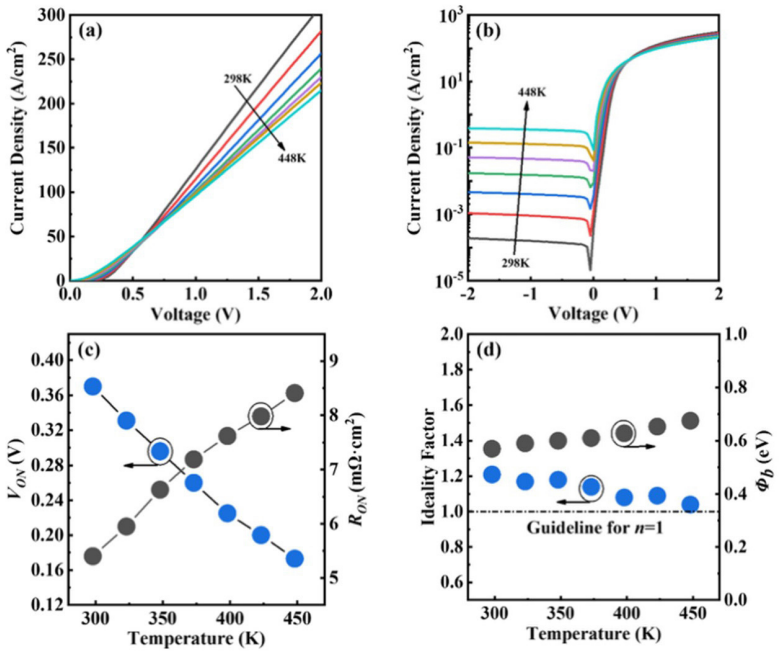

△ 图5:在298至473 K范围内测量的具有OPT(直径= 100 um)的垂直GaN SBD与温度相关的(a)正向J-V特性和(b)反向J-V特性。(c)VON和RON作为具有OPT的垂直GaN SBD的温度函数。(d)采用OPT的垂直GaN SBD的理想因子和肖特基势垒高度与温度的函数关系。

△ 图5:在298至473 K范围内测量的具有OPT(直径= 100 um)的垂直GaN SBD与温度相关的(a)正向J-V特性和(b)反向J-V特性。(c)VON和RON作为具有OPT的垂直GaN SBD的温度函数。(d)采用OPT的垂直GaN SBD的理想因子和肖特基势垒高度与温度的函数关系。

图5(a)显示了在298 K至473 K范围内测量的具有OPT的GaN SBD的随温度变化的正向J-V特性。结果表明,器件在正向电压下表现出很强的温度依赖性,并且电流密度随着温度的升高而降低。[24]在298 K至473 K范围内测量的OPT器件随温度变化的反向J-V特性如图5(b)所示,在反向电压下,器件表现出良好的整流特性和明显的温度依赖性。器件的反向漏电流随着温度的升高而增大,表明电子在高温下获得了更高的能量来克服SBH,这种现象与TE模型的特征一致。[28]图5(c)显示了具有OPT的器件的VON和RON作为温度的函数。温度越高,设备打开的速度越快。导通电压VON电压从0.37 V降低到0.17 V,这是由于电子的扩散速率随着温度的升高而增加,更多的电子可能穿过势垒或发生隧道效应。同时,随着温度的升高,器件的RON也相应增大。[29-33]图5(d)分别显示了理想因子n和肖特基势垒Φb与温度T的函数。

△ 图6:(a)VF = 5 V时的脉冲V-T和脉冲I-T,(b)IF(VF = 5 V时)作为应力时间的函数,(c)VF(J = 500 A/cm2时)作为应力时间的函数298 K和423 K下应力时间的函数,以及(d)VF(J =500 A/cm2)作为具有OPT的垂直GaN SBD在298 K和423 K下应力时间的函数。(e)垂直和横向GaN SBD的VON与BFOM基准的开启电压与BFOM的关系。

△ 图6:(a)VF = 5 V时的脉冲V-T和脉冲I-T,(b)IF(VF = 5 V时)作为应力时间的函数,(c)VF(J = 500 A/cm2时)作为应力时间的函数298 K和423 K下应力时间的函数,以及(d)VF(J =500 A/cm2)作为具有OPT的垂直GaN SBD在298 K和423 K下应力时间的函数。(e)垂直和横向GaN SBD的VON与BFOM基准的开启电压与BFOM的关系。

为了研究采用OPT的GaN SBD的可靠性,图6(a)显示了正向电压VF = 5 V时的低应力脉冲,占空比固定为50%,周期为1 ms,占空比为固定在50%是因为模拟器的实际工作状态,50%时间在充电,50%时间在放电,如果占空比调制到1%或0.1%,脉冲时间太短,会偏离实际工作设备的状况。将静态电压设置为0 V不仅可以模拟非工作电压,还可以缓解内部空穴积累,减少下一脉冲对阈值电压的影响。图6(b)是从图6(a)中提取的经过1 s、10 s、100 s和1000 s长时间应力后的结果,轻微的变化表明器件具有较高的可靠性。图6(c)和(d)显示了VF(定义为500 A/cm2下的J)与298 K和423 K应力时间之间的关系,VF是在电压分别为4 V和-100V下应力后获得的。器件在不同应力时间下的劣化变化不大(5%以下),没有明显的规律性。两种脉冲测试表明,采用OPT的垂直GaN SBD具有鲁棒且高可靠性的性能。OPT GaN SBD的Baliga品质因数(BFOM = BV2/RON)为1.78×108 W·cm-2。图6(e)分别显示了垂直和横向GaN SBD的VON VS与BFOM的基准。[34-39]与报道的垂直GaN SBD相比,本工作中使用OPT制造的器件实现了0.37 V的超低VON。BFOM受限于681V的击穿电压。根据平行面击穿极限[40],在非击穿条件下,击穿电压受到漂移区20 μm厚度和~1.51×1016 cm-3掺杂浓度的限制。FGR的结构还有待优化。

总之,本工作中通过OPT制造了具有超低VON(0.37V)的垂直GaN SBD。垂直GaN SBD的VBR为681 V(J = 1 A/cm2),RON为2.6 mΩ·cm2。低应力脉冲测试和高应力脉冲测试均表明采用OPT的垂直GaN SBD坚固可靠。结果表明,这些器件在100 V以下的低功耗应用中具有巨大潜力。

致谢

该工作得到国家自然科学基金(61974144, 62004127)、广东省重点领域研发计划(2020B010169001)、广东省杰出青年科学基金(2022B1515020073)、深圳市科技计划(JCYJ20220818102809020)的资助)。我们感谢深圳大学电子显微镜中心在 HRTEM 观察方面以及深圳大学光子学研究中心的器件制造过程方面提供的帮助。

利益冲突

作者没有需要披露的利益冲突。

数据可用性

支持本研究结果的数据可根据合理要求从通讯作者处获得。

扩展阅读

1. X. Guo, Y. Zhong, J. He, Y. Zhou, S. Su, X. Chen, J. Liu, H. Gao, X. Sun, Q. Zhou, Q. Sun, and H. Yang, “High-Voltage and High-ION/IOFF Quasi-Vertical GaN-on-Si Schottky Barrier Diode With Argon-Implanted Termination,” IEEE Electron Device Lett. 42, 473 (2021).

2. X. Liu, F. Lin, J. Li, Y. Lin, J. Wu, H. Wang, X. Li, S. Huang, Q. Wang, H.-C. Chiu, 11 and H.-C. Kuo, “1.7-kV Vertical GaN-on-GaN Schottky Barrier Diodes With Helium-Implanted Edge Termination,” IEEE Trans. on Electron Devices 69, 1938 (2022).

3. H. Fu, K. Fu, S. Chowdhury, T. Palacios, and Y. Zhao, “Vertical GaN Power Devices: Device Principles and Fabrication Technologies—Part I,” IEEE Trans. on Electron Devices 68, 3200 (2021).

4. Matteo Meneghini, Carlo De Santi, Idriss Abid, Matteo Buffolo, Marcello Cioni, Riyaz Abdul Khadar, Luca Nela, Nicolò Zagni, Alessandro Chini, Farid Medjdoub, Gaudenzio Meneghesso, Giovanni Verzellesi, Enrico Zanoni; Elison Matioli, “GaN-based power devices: Physics, reliability, and perspectives,” J. APPL. PHYS. 130, 181101 (2021).

5. T. Pu, U. Younis, H. C. Chiu, K. Xu, H. Kuo, and X. Liu, “Review of Recent Progress on Vertical GaN-Based PN Diodes,” Nanoscale Res. Lett. 16 (1), 14 (2021).

6. Y. Sun, X. Kang, Y. Zheng, J. Lu, X. Tian, K. Wei, H. Wu, W. Wang, X. Liu, and G. Zhang, “Review of the Recent Progress on GaN-Based Vertical Power Schottky Barrier Diodes (SBDs),” Electronics 8, 575 (2019).

7. L. Cheng, K. Zhou, Z. Zhang, G. Zhang, Z. Yang, and Y. Tong, “Occurrence of cubic GaN and strain relaxation in GaN buffer layers grown by low-pressure metalorganic vapor phase epitaxy on (0001) sapphire substrates,” Appl. Phys. Lett. 74, 661 (1999).

8. K. J. Chen, O. Haberlen, A. Lidow, C. L. Tsai, T. Ueda, Y. Uemoto, Y. Wu, “GaN-on-Si Power Technology: Devices and Applications,” IEEE Trans. Electron Devices, 64, 779 (2017).

9. S. Han, S. Yang, and K. Sheng, “Fluorine-Implanted Termination for Vertical GaN Schottky Rectifier With High Blocking Voltage and Low Forward Voltage drop,” IEEE Electron Device Lett. 40, 1040 (2019).

10. H. Fu, X. Huang, H. Chen, Z. Lu, I. Baranowski, and Y. Zhao, “Ultra-low turn-on voltage and on-resistance vertical GaN-on-GaN Schottky power diodes with high mobility double drift layers,” Appl. Phys. Lett. 111, 152102 (2017).

11. X. Guo, Y. Zhong, Y. Zhou, S. Su, X. Chen, S. Yan, J. Liu, X. Sun, Q. Sun, and H. Yang, “Nitrogen-Implanted Guard Rings for 600-V Quasi-Vertical GaN-on-Si Schottky Barrier Diodes With a BFOM of 0.26 GW/cm2,” IEEE Trans. on Electron Devices 68, 5682 (2021).

12. J. Chen, Z. Liu, Z. Bian, H. Wang, X. Duan, J. Ning, J. Zhang, and Y. Hao, “Nearly ideal quasi-vertical GaN Schottky barrier diode with 1010 high on/off ratio and ultralow turn on voltage via post anode annealing,” in 2021 5th IEEE Electron Devices Technology & Manufacturing Conference (EDTM), 1 (2021).

13. X. Kang, X. Wang, S. Huang, J. Zhang, J. Fan, S. Yang, Y. Wang, Y. Zheng, K. Wei, and J. Zhi, “Recess-free AlGaN/GaN lateral Schottky barrier controlled Schottky rectifier with low turn-on voltage and high reverse blocking.” Proceedings of the 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 280 (2018).

14. J.-G. Lee, B.-R. Park, C.-H. Cho, K.-S. Seo, and H.-Y. Cha, “Low Turn-On Voltage AlGaN/GaN-on-Si Rectifier With Gated Ohmic Anode,” IEEE Electron Device Lett. 34, 214-216 (2013).

15. Y. Zhang, J. Zhang, H. Zhou, T. Zhang, H. Wang, Z. Feng, and Y. Hao, “Leakage current mechanisms of groove-type tungsten-anode GaN SBDs with ultra low turn-ON voltage and low reverse current,” Solid-State Electron. 169, 107807 (2020).

16. H. Woo, J. Lee, Y. Jo, J. Han, J. Kim, H. Kim, C. H. Roh, J. H. Lee, J. Park, C.-K. Hahn, and H. Im, “Barrier lowering and leakage current reduction in Ni-AlGaN/GaN Schottky diodes with an oxygen-treated GaN cap layer,” Current Appl. Phys. 15, 1027, (2015).

17. M. Hua, J. Wei, G. Tang, Z. Zhang, Q. Qian, X. Cai, N. Wang, and K. J. Chen, “Normally-off LPCVD-SiNx/GaN MIS-FET with crystalline oxidation interlayer,” IEEE Electron Device Lett. 38, 929 (2017).

18. Z. Bian, J. Zhang, S. Zhao, Y. Zhang, X. Duan, J. Chen, J. Ning, and Y. Hao, “1.48MV.cm-1/0.2 mOmega.cm2 GaN Quasi-Vertical Schottky Diode via Oxygen Plasma Termination,” IEEE Electron Device Lett. 41, 1476 (2020).

19. R. Yin, Y. Li, C. P. Wen, Y. Fu, Y. Hao, M. Wang, and B. Shen, “High voltage vertical GaN-on-GaN Schottky barrier diode with high energy fluorine ion implantation based on space charge induced field modulation (SCIFM) effect,” 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), 298 (2020).

20. Y. Zhang, M. Sun, Z. Liu, D. Piedra, M. Pan, X. Gao, Y. Lin, A. Zubair, L. Yu, and T. Palacios, “Novel GaN trench MIS barrier Schottky rectifiers with implanted field rings,” 2016 IEEE International Electron Devices Meeting (IEDM), 10.2.1 (2016).

21. Y. Cao, R. Chu, R. Li, M. Chen, R. Chang, and B. Hughes, “High-voltage vertical GaN Schottky diode enabled by low-carbon metal-organic chemical vapor deposition growth,” Appl. Phys. Lett. 108, 5 (2016).

22. S.-C. Lee, J.-C. Her, S.-S. Kim, M.-W. Ha, K.-S. Seo, Y.-I. Choi, M.-K. Han, “A new vertical GaN Schottky barrier diode with floating metal ring for highbreakdown voltage,” 2004 16th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 319 (2004).

23. S.-C. Lee, M.-W. Ha, J.-C. Her, S.-S. Kim, J.-Y. Lim, K.-S. Seo, M.-K. Han, “High breakdown voltage GaN Schottky barrier diode employing floating metal rings on AlGaN/GaN hetero-junction,” 2005 The 17th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 247 (2005).

24. Tsung-Han Yang, Houqiang Fu, Kai Fu, Chen Yang, Jossue Montes, Xuanqi Huang, Hong Chen, Jingan Zhou, Xin Qi, Xuguang Deng, Yuji Zhao, “Vertical GaN-on-GaN Schottky Barrier Diodes with Multi-Floating Metal Rings,” IEEE J. Electron Dev. 8, 857 (2020).

25. J. Chen, J. Zhao, S. Feng, L. Zhang, Y. Cheng, H. Liao, Z. Zheng, X. Chen, Z. Gao, K. J. Chen, M. Hua, “Formation and applications in electronic devices of lattice-aligned gallium oxynitride nanolayer on gallium nitride,” Adv. Mater. e2208960 (2023).

26. Maeda T, Okada M, Ueno M, Yamamoto Y, Kimoto T, Horita M, and Suda J, “Temperature dependence of barrier height in Ni/n-GaN Schottky barrier diode,” Appl. Phys. Express 10, 051002 (2017).

27. Suda J, Yamaji K, Hayashi Y, Kimoto T, Shimoyama K, Namita H, and Nagao S, “Nearly ideal current–voltage characteristics of Schottky barrier diodes formed on hydride-vapor-phase-epitaxy-grown GaN free-standing substrates,” Appl. Phys. Express 3, 101003 (2010).

28. Saitoh Y, Sumiyoshi K, Okada M, Horii T, Miyazaki T, Shiomi H, Ueno M, Katayama K, K Makoto, Nakamura T, “Extremely low on-resistance and high breakdown voltage observed in vertical GaN Schottky barrier diodes with high-mobility drift layers on low-dislocation-density GaN substrates,” Appl. Phys. Express 3, 081001 (2010).

29. L. A. Li, X. B. Li, T. F. Pu, S. H. Cheng, H. D. Li, and J. P. Ao, “Vertical GaN-Based Temperature Sensor by Using TiN Anode Schottky Barrier Diode,” IEEE Sens. J. 21, 1273 (2021).

30. S. Han, S. Yang, and K. Sheng, “High-Voltage and High-ION/IOFF Vertical GaN-on-GaN Schottky Barrier Diode With Nitridation-Based Termination,” IEEE Electron Device Lett. 39, 572 (2018).

31. E. Acurio, F. Crupi, N. Ronchi, B. De Jaeger, B. Bakeroot, S. Decoutere, and L. Trojman, “Reliability Improvements in AlGaN/GaN Schottky Barrier Diodes With a Gated Edge Termination,” IEEE Trans. on Electron Devices 65, 1765 (2018).

32. E. Acurio, L. Trojman, F. Crupi, T. Moposita, B. De Jaeger, and S. Decoutere, “Reliability Assessment of AlGaN/GaN Schottky Barrier Diodes Under ON-State Stress,” IEEE Trans. on Device and Mat. Re. 20, 167 (2020).

33. A. N. Tallarico, S. Stoffels, P. Magnone, J. Hu, S. Lenci, D. Marcon, E. Sangiorgi, C. Fiegna, and S. Decoutere, “Reliability of Au-Free AlGaN/GaN-on-Silicon Schottky Barrier Diodes Under ON-State Stress,” IEEE Trans. on Electron Devices 63, 723 (2016).

34. X. Wei, W. Shen, X. Zhou, W. Tang, Y. Ma, T. Chen, D. Wang, H. Fu, X. Zhang, W. Lin, G. Yu, Y. Cai, and B. Zhang, “2.69 kV/2.11 mΩ·cm2 and Low Leakage p-GaN Stripe Array Gated Hybrid Anode Diodes With Low Turn-on Voltage,” IEEE Electron Device Lett. 44, 13 (2023).

35. M. Xiao, Y. Ma, K. Cheng, K. Liu, A. Xie, E. Beam, Y. Cao, and Y. Zhang, “3.3 kV Multi-Channel AlGaN/GaN Schottky Barrier Diodes With P-GaN Termination,” IEEE Electron Device Lett. 41, 1177 (2020).

36. T. Zhang, J. Zhang, H. Zhou, Y. Zhang, T. Chen, K. Zhang, Y. Wang, K. Dang, Z. Bian, X. Duan, J. Ning, S. Zhao, and Y. Hao, “High-performance lateral GaN Schottky barrier diode on silicon substrate with low turn-on voltage of 0.31 V, high breakdown voltage of 2.65 kV and high-power figure of-merit of 2.65 GW cm-2,” Appl. Phys. Express 12, 046502 (2019).

37. R. Xu, P. Chen, M. Liu, J. Zhou, Y. Li, K. Cheng, B. Liu, D. Chen, Z. Xie, R. Zhang, and Youdou Zheng, “3.4-kV AlGaN/GaN Schottky Barrier Diode on Silicon Substrate With Engineered Anode Structure,” IEEE Electron Device Lett. 42, 208 (2021).

38. R. Xu, P. Chen, M. Liu, J. Zhou, Y. Li, B. Liu, D. Chen, Z. Xie, R. Zhang, Y. Zheng, “2.7-kV AlGaN/GaN Schottky barrier diode on silicon substrate with recessed-anode structure,” SOLID STATE ELECTRON 175, 107953 (2021).

39. T. Zhang, J. Zhang, H. Zhou, T. Chen, K. Zhang, Z. Hu, Z.e Bian, K. Dang, Y. Wang, L. Zhang, J. Ning, P. Ma, and Y. Hao, “A 1.9-kV/2.61-mΩ·cm2 Lateral GaN Schottky Barrier Diode on Silicon Substrate With Tungsten Anode and Low Turn-ON Voltage of 0.35 V,” IEEE Electron Device Lett. 39, 1548 (2018).

40. T. Maeda, T. Narita, S. Yamada, T. Kachi, T. Kimoto, M. Horita, and J. Suda, “Impact ionization coefficients and critical electric field in GaN,” J. Appl. Phys. 129, 185703 (2021).

| 上一篇:基于NX封装的低杂感SiC... | 下一篇:半绝缘半导体电阻率、迁... |