氮化镓功率集成电路技术

2024/8/28 15:58:31 材料来源:ACT化合物半导体

作者:李思超、何俊蕾、李成果、叶刚、赵波、葛晓明、贾汉祥、卢双赞、潘磊、胡昌宇、王瑜璞,九峰山实验室

从分立器件到集成电路

相较于传统体硅材料制造的功率器件,以GaN、SiC为代表的第三代化合物半导体凭借其卓越的电流密度及击穿电压,逐渐成为下一代功率开关器件。这其中GaN HEMT又具备高频高速的开关能力,能大幅度缩小电容、电感、变压器等无源元件的体积,从而提升电源系统整体功率密度,并进一步促进了电力电子系统往小型化、轻量化的方向发展。GaN正逐步被应用于各类体积紧凑型场景中,如手机充电器、便携笔记本电脑的适配器、数据中心的供电电源、无人机的电机驱动等。

在传统电力电子系统中,功率器件与周边的驱动器、控制器以及负载等均以分立元件的形式焊接在同一PCB板上,而功率器件与这些功能元件之间存在的传输路径会带来寄生电感,这部分寄生电感除了会抑制GaN高频高速开关的核心优势以外,还会带来效率降低、电磁干扰、通讯延迟以及可靠性风险等诸多问题。

为了克服分立功率元件的诸多弊端,通过将电力电子系统中各功能组件进行集成,能够最大程度发挥GaN器件高频高速开关特性,并能提升传输效率、保证通讯完整性、加固系统可靠性以及增强元件间的匹配度。而不同层次的集成度将会带来不一样的收益:(1)将功率器件与驱动、传感及控制电路集成,能增强通讯完整性与一致性,并降低电源系统设计者设计难度;(2)将功率器件集成为单芯片功率转换电路,能降低器件过冲电压,增强系统的可靠性与鲁棒性;(3)将功率转换电路与用电负载进行集成,能降低电能传输过程中电压降低,提升传输效率。

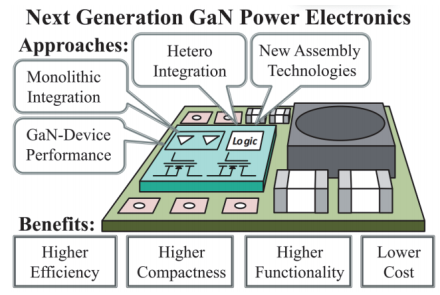

△ 图1:下一代GaN功率集成电路,包括功率器件、驱动电路、数字电路等[1]。

如同传统硅基BCD工艺一样,水平结构的GaN HEMT器件使其便于在同一颗芯片上集成多功能元件。如图1所示,GaN功率开关器件与外围功能单元组合成功率单片集成电路,并可通过先进封装与其他组件实现异质集成,共同构建更高效、更紧凑、功能更全面、成本更低的下一代电力电子系统。GaN功率器件构建的集成程度主要分四个类型:(1)驱动电路集成,主要指功率器件与外围功能单元包括驱动、传感、保护等进行集成。(2)功率器件集成,主要指将两个及以上功率器件,集成到单一芯片上,以实现不同拓扑结构的功率换流器,如H桥换流器、多相换流器、多级换流器。(3)逻辑电路集成,主要指将控制器、界面等数字单元进行集成。(4)负载集成,主要指将电能转换系统与负载直接进行异质集成,如将GaN供电模块与CPU/GPU核集成,构成GaN-on-CMOS。除此以外,GaN功率集成还可以同能量存储单元或能量收集单元进行集成,构建完整的集成电源系统。

驱动单片集成

尽管GaN HEMT功率器件作为高频高速开关的优势明显,但当器件工作在快速开关状态时仍然存在诸多挑战:如栅极电压过冲、误导通以及检测响应延迟等。所有这些问题都阻碍了GaN HEMT作为高频高速开关的潜力,使其作为下一代功率开关的优势并未发挥到极致。

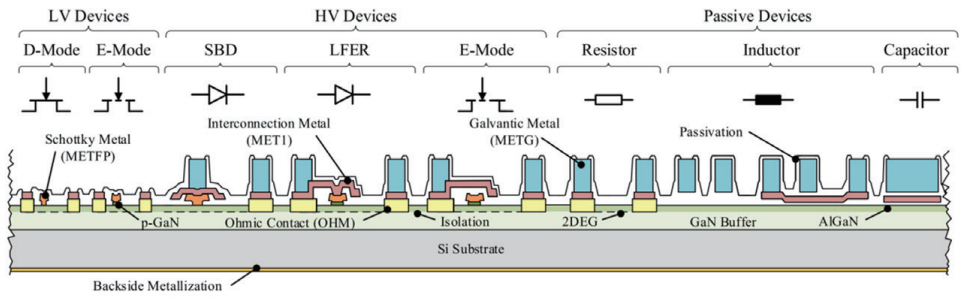

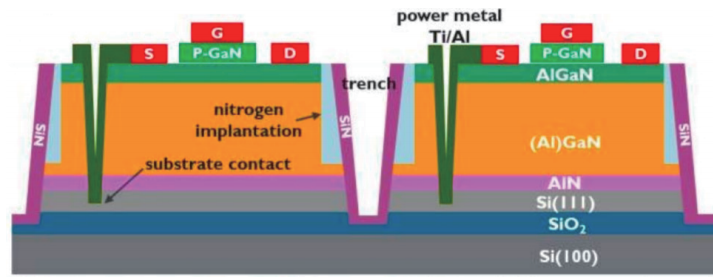

△ 图2:基于硅基GaN技术的功率集成电路平台的各元件的截面图[5]。

△ 图2:基于硅基GaN技术的功率集成电路平台的各元件的截面图[5]。

2009年,香港科技大学首次基于GaN HEMT平台构建GaN智能功率集成平台[2]。通过氟等离子体注入实现增强型GaN功率器件,并实现器件间的水平电气隔离,首次在GaN-on-Si外延上实现了高压功率器件与外围数模混合电路的集成。但是,由于基于氟负离子构建的增强型栅极稳定性较弱,无法大规模量产。如图2所示,该图为日本松下公司和德国Fraunhofer应用固态物理研究所提出的“基于p-GaN栅结构的增强型GaN功率器件实现的功率集成电路平台[3-5]”。这种结构在工艺上更容易实现,器件特性也更加稳定可靠。

目前,商用的高压集成驱动器件主要应用在650-700V电压等级之间。Navitas的All GaNTM系列,将650V GaN功率器件、驱动、dV/dt控制以及欠压保护(ULVO)等功能集成到单颗GaN功率集成电路中[6]。此外,英国Cambridge GaN器件公司也推出其ICeGaNTM平台,集成了功率器件、检测、保护电路以及用于安全快速关断的米勒钳位电路[7]。

低压集成驱动器件则主要应用在40-100V电压等级之间,代表厂商为EPC,其推出的40-100V单片集成功率驱动电路[8],主要包含两类系列产品:(1)半桥驱动电路ePowerTM系列,集成了驱动、电平位移、欠压保护等功能,最高开关频率可达3 MHz。(2)用于40-100 V激光雷达驱动的eToFTM系列,与驱动电路集成,实现最高开关频率达10-200 MHz,将GaN功率开关器件的开关频率推到极致。

功率单片集成

将两个及以上功率器件,集成到单一芯片上,可以实现不同拓扑结构的功率换流器,如H桥换流器、多相换流器、多级换流器。通常,为降低成本,功率器件之间会共用同一体硅材料作为衬底,这就会导致功率器件受到衬偏效应的影响,进而造成功率器件阈值电压漂移、动态电阻恶化、等效电容增加等问题。为了抑制衬偏效应,各功率器件的衬底之间需要进行电气隔离。电气隔离主要分为两个维度,横向隔离和纵向隔离。其中,横向隔离主要采用深槽刻蚀工艺,并以填充介质的方式实现。衬底纵向隔离的方法主要有两大类:(1)使用价格便宜的硅衬底,同时对硅衬底进行工程化设计,如形成PN结进行隔离,此外,也可通过增加衬底屏蔽层等方式实现衬底纵向隔离。(2)使用绝缘型衬底如SOI衬底或蓝宝石衬底,利用天然绝缘层实现衬底纵向隔离。

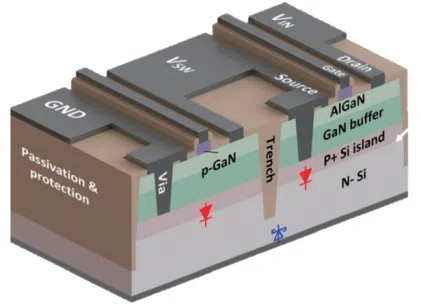

△ 图3:基于工程化体硅衬底的GaN功率集成技术示意图[9]。

香港科技大学提出通过低成本的方式对硅衬底进行工程化处理(EBUS),即在n型硅衬底表面通过离子注入方式形成p型层,随后在该衬底上外延生长GaN HEMT结构,形成GaN-on-EBUS。由于硅衬底内引入了内建PN结,实现了器件间的纵向电气隔离[9]。如图3所示,为存在PN结的硅衬底上外延GaN层,并通过深槽刻蚀工艺将每个功率器件分隔为不同的小岛,进而实现横向隔离,每个小岛的衬底电位都是相互独立,并与其余衬底电位之间形成电气隔离。

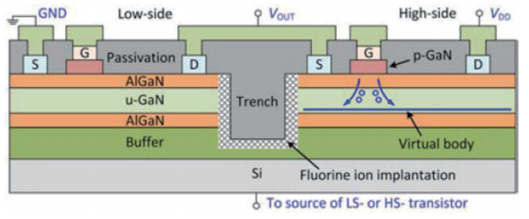

△ 图4:基于虚体屏蔽层的GaN功率集成技术示意图[10]。

△ 图4:基于虚体屏蔽层的GaN功率集成技术示意图[10]。

如图4所示,为北京大学提出在外延层中引入虚体屏蔽层,该结构不仅可以阻隔衬底间的串扰,还能防止电子被缓冲层捕获而引发动态电阻恶化[10]。在开启状态下,p-GaN栅极区域注入空穴到下方虚体层,并在虚体层中扩散开来形成屏蔽层。这种由空穴构建的屏蔽层,一方面可实现衬底的纵向隔离,抑制衬偏效应,另外一方面也可以与热电子进行复合,减少电子进入缓冲层而被缺陷捕获。此外空穴与电子复合后形成的光子还能加速表面缺陷的恢复。

除了上述基于GaN-on-Si构架下的功率集成技术,另外还有利用绝缘夹层或绝缘型衬底来实现衬底隔离。如下图5所示,为IMEC提出的基于GaN-on-SOI技术,利用埋层氧化硅层对衬底进行纵向隔离,并通过深槽刻蚀工艺实现功率器件间的横向隔离[11]。尽管埋层氧化硅有效地阻隔了衬底电压的影响,但由于其热导率较低,导致功率器件工作过程中的热量较难从衬底散出。

△ 图5:GaN-on-SOI单片功率集成平台示意图[11]。

△ 图5:GaN-on-SOI单片功率集成平台示意图[11]。

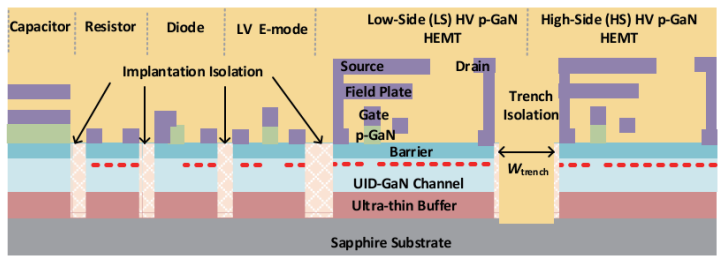

另外一种方式是利用本身即为绝缘体的蓝宝石衬底进行功率器件间的电气隔离。如下图6所示,为东南大学与江苏能华微电子在基于蓝宝石衬底外延的GaN层上实现的功率半桥电路的单片集成示意图,耐压等级达到了3000V以上[12]。相比于SOI衬底,蓝宝石衬底上功率器件基准化击穿电压增加了40%。正是由于蓝宝石衬底高电压阻断特性,通常也被用来实现超高压GaN功率器件。然而,蓝宝石同SOI相似,导热率很低,约为硅的1/6,且目前商用的蓝宝石衬底尺寸一般为6寸,制造成本上将会是一个挑战。

△ 图6:GaN-on-Sapphire单片功率集成平台示意图[12]。

△ 图6:GaN-on-Sapphire单片功率集成平台示意图[12]。

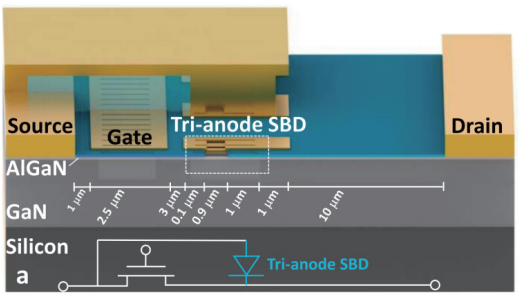

△ 图7:GaN MOS-HEMT集成鱼鳍肖特基阳极续流二极管[13]。

△ 图7:GaN MOS-HEMT集成鱼鳍肖特基阳极续流二极管[13]。

除了上述开发的各种衬底纵向隔离技术,以实现功率开关器件单片集成外,还有一部分研究集中在将反向续流二极管与功率管进行集成,主要的原因是GaN HEMT器件没有如硅MOS一样的内建PN结。如图7所示,为洛桑联邦理工提出了将鱼鳍肖特基阳极二极管反向并联到MOS-HEMT器件的栅漏之间,从而实现GaN器件具有反向续流能力[13]。

逻辑电路集成

将GaN开发成如硅一样的CMOS逻辑电路一直以来都存在巨大的挑战,这主要受限于GaN缺少一种能同时将p型沟道与n型沟道集成到单一芯片上的构架。这是因为GaN材料体系中空穴迁移率(15 cm2 /V.s)与电子迁移率(2000 cm2 /V.s)的悬殊较大,无法实现良好的器件尺寸匹配。

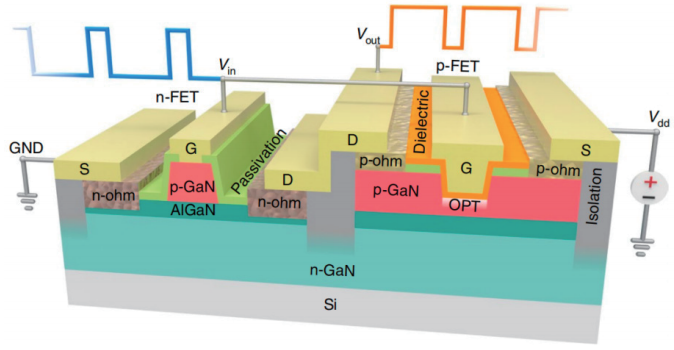

△ 图8:基于商用p-GaN栅功率器件平台构建的GaN互补型反相器[14]。

△ 图8:基于商用p-GaN栅功率器件平台构建的GaN互补型反相器[14]。

如图8所示,香港科技大学基于p-GaN栅HEMT外延层实现p型沟道,与HEMT中的二维电子气形成互补型逻辑电路[14]。为更好提高p型沟道迁移率,研究团队利用氧等离子对p-GaN区域进行处理,但相较于n型沟道器件(电流密度~170mA/mm),p型沟道器件的电流输运能力仍较弱(~1.64 mA/mm)。尽管如此,基于此互补型逻辑构建的单级反相器仍表现出低静态功耗、低转换时间、高电压增益、大噪声容限、高热稳定性等优势。

此外,MIT相关研究团队提出利用MOCVD生长出同时存在n型和p型沟道的外延结构,并通过垂直互补形成CMOS电路[15]。相比于传统p-GaN栅外延层,其团队加入p型迁移率增强层和散射屏蔽层,来提升其p型沟道迁移率。同时,从器件结构上通过缩短栅极长度来提升电流密度,并基于鱼鳍栅提升栅极控制能力。其p型沟道器件的电流密度可高达300 mA/mm,接近0.13 μm Si BCD工艺。

Si/GaN异质集成

尽管,上述基于不同构架实现了GaN功率器件与模拟电路及数字电路的单片集成,然而基于GaN材料构建的大规模集成电路仍然存在静态功耗较大,芯片面积较大等问题。为充分发挥Si CMOS和GaN功率器件各自的优势,另一种方式是将Si CMOS和GaN换流器进行异质集成,其主要做法也从二维模式逐渐过渡到三维模式:(1)Si CMOS与GaN功率器件之间通过基板进行水平连接。GaN供电单元与硅器件通过封装或焊锡的方式贴在同一块PCB上,这种连接距离通常要到毫米甚至厘米量级,因此会引入较大的寄生参数;(2)Si CMOS与GaN功率器件通过背对背的方式实现垂直堆叠。这种方式将传输距离降低到百微米级,但需要较深的硅通孔,制造工艺更为复杂,成本也更高;(3)Si CMOS与GaN功率器件通过面对面的混合键合形成电气连接,如图9所示[16]。这种构架下的传输距离最近,仅为几个微米,同时可用背面硅衬底进行散热。

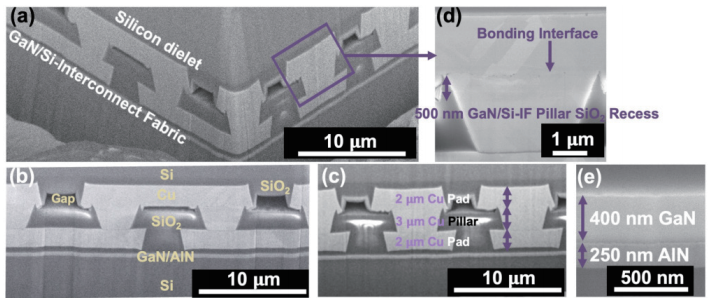

△ 图9:Si芯粒与GaN-on-Si芯粒的混合键合的(a)3D截面图;(b)(c)x和y方向上±1 μm的对准精度;(d)Cu-Cu键合界面的放大图;(e)GaN/AlN外延层的放大图[16]。

△ 图9:Si芯粒与GaN-on-Si芯粒的混合键合的(a)3D截面图;(b)(c)x和y方向上±1 μm的对准精度;(d)Cu-Cu键合界面的放大图;(e)GaN/AlN外延层的放大图[16]。

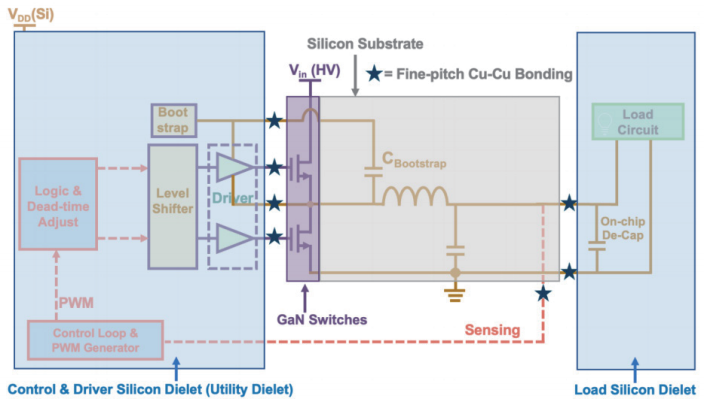

△ 图10:通过键合实现GaN功率集成电路与Si控制/驱动/负载芯粒之间的异质集成[16]。

△ 图10:通过键合实现GaN功率集成电路与Si控制/驱动/负载芯粒之间的异质集成[16]。

如图10所示,UCLA提出通过上述混合键合的方式将Si控制器或驱动电路倒装键合至GaN电源转换系统芯粒上(CMOS-on-GaN),甚至更进一步,将GaN电源转换芯粒与负载芯粒直接进行混合键合[16]。这样短距离的异质集成方式,不仅降低了栅极驱动环路寄生电感和栅极振铃,也缩短了负载供电路径,避免了电压降,提高了能量转换效率。

GaN功率集成电路技术展望

后摩尔时代下,无论是Si CMOS,III-V族光电器件,还是通信芯片或存储单元都朝着高能量密度的方向发展,而这些离不开与之匹配的高功率密度电能转换单元。GaN凭借其高击穿电压和高电流密度,能够实现高功率密度输出,无论是同质单片集成,还是通过紧凑型异质集成方法,未来GaN功率集成电路将推动能量转换系统朝着低功耗、高效率、紧凑体积的方向发展,推动下一代电力电子器件的发展。

九峰山实验室针对现有功率技术发展方向和产业痛点,积极开展8寸硅基GaN单片集成及异质集成平台能力建设,已建成产业研发级的基础设施,布局功能全面和性能先进的设备资源。面向硅基GaN功率集成电路的技术需求,开发核心技术。九峰山实验室积极拓展合作伙伴,期望与同行业一起构架功率集成技术的领先。

扩展阅读

[1] R. Reiner, M. Basler, S. Moench et al. Lateral GaN Power Devices and Integrated GaN Power Circuits: Status and Recent Progress. in: Bauelemente der Leistungselektronik und ihre Anwendungen, 2023.

[2] K. Wong, W. Chen, K. Chen. Integrated Voltage Reference and Comparator Circuits for GaN Smart Power Chip Technology. in: IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2009.

[3] Y. Uemoto, T. Morita, A. Ikoshi et al. GaN Monolithic Inverter IC Using Normally-off Gate Injection Transistors with Planar Isolation on Si Substrate. in: IEEE International Electron Devices Meeting (IEDM), 2009.

[4] R. Reiner, P. Waltereit, B. Weiss et al. Monolithic Integrated Power Circuit in High-voltage GaN-on-Si Heterojunction Technology. in: IET Power Electron, 11(4), 2018.

[5] M. Basler, R. Reiner, S. Moench et al. Building Blocks for GaN Power Integration. in: IEEE Access, 9, 2021.

[6] D. Kinzer. Monolithic GaN Power IC Technology Drives Wide Bandgap Adoption. in: IEEE International Electron Devices Meeting (IEDM), 2020.

[7] F. Udrea, M. Arnoald, L. Efthymiou et al. The Smart ICeGaN Platform with Sensing and Protection Functions for Both Enhanced Ease of Use and Gate Reliability. in: IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2022.

[8] A. Lidow. The Path Forward for GaN Power Devices. in: IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), 2020.

[9] G. Lyu, J. Wei, W. Song et al. GaN on Engineered Bulk Si (GaN-on-EBUS) Susbtrate for Monolithic Integration of High-/Low-Side Switches in Bridge Circuits. in: IEEE Transactions on Electron Devices, 69(8), 2022.

[10] J. Yang, J. Wei, M. Wang et al. 650-V GaN-on-Si Power Integration Platform Using Virtual-Body p-GaN Gate HEMT to Screen Substrate-Induced Crosstalk. in: IEEE International Electron Devices Meeting (IEDM), 2023.

[11] X. Li, M. Hove, M. Zhao et al. Enhancement-Mode p-GaN HEMTs Fabricated on 200 mm GaN-on-SOI With Trench Isolation for Monolithic Integration. in: IEEE Electron Device Letters, 38(7), 2017.

[12] S. Li, Y. Ma, W. Lu et al. 1200 V E-mode GaN Monolithic Integration Platform on Sapphire with Ultra-thin Buffer Technology. in: IEEE International Electron Devices Meeting (IEDM), 2023.

[13] T. Wang, J. Ma, E. Matioli et al. 1100 V AlGaN/GaN MOSHEMTs With Integrated Tri-Anode Freewheeling Diodes. in: IEEE Electron Device Letters, 39(7), 2018.

[14] Z. Zheng, L. Zhang, W. Song et al. Gallium Nitride-based Complementary Logic Integrated Circuits. in Nature Electronics, 4, 2021.

[15] Q. Xie, M. Yuan, J. Niroula et al. Highly Scaled GaN Complementary Technology on a Silicon Substrate. in: Transactions on Electron Devices, 70(4), 2023.

[16] H. Ren, K. Sahoo, Z. Guo et al. Heterogeneous Power Delivery for Large Chiplet-based Systems using Integrated GaN/Si-Interconnect Fabric with sub-10 um Bond Pitch. in: IEEE International Electron Devices Meeting (IEDM), 2023.

| 上一篇:转向单片多色microLED阵... | 下一篇:利用USACH BoulePro-20... |