SiC超结的一种卓越工艺

2025/1/3 15:40:43 材料来源:ACT化合物半导体

多轮超高能注入和外延生长能够让SiC超结器件阻断数千伏电压

多轮超高能注入和外延生长能够让SiC超结器件阻断数千伏电压

作者:Reza Ghandi,GE Research

减少全球碳足迹,必须大力改善电力基础设施。除了需要增加可再生能源发电比例相关的优先事项以外,还需要提高从发电地到使用地的电力传输效率。

电力基础设施的关键部分是中压电力转换系统,该系统可用于风力涡轮机、太阳能装置和舰船用转换器。由于硅基固态开关和二极管的损耗,此类功率转换系统在3.3kV以上的电压下工作,其开关频率仅限于数百赫兹以下。而这与理想相差甚远,因为在低频下,变压器和转换器滤波器的重量可能高达数吨,增加了系统成本和安装成本并限制了设计的灵活性。因此,我们需要转向基于超高压功率半导体器件的高效、轻量、多兆瓦及多千赫功率转换系统,该类器件开关为中等频率(例如1-20kHz)。

如果长期关注本杂志,您就会了解SiC器件可以解决现有硅基器件的许多局限性。而在几千伏的阻断电压下,利用此种方法取得的成功至关重要。在3.3kV及以上的阻断电压下,SiC单极开关和二极管在高温下会遭受高传导损耗,而SiC双极器件(例如IGBT)表现出3V的高正向压降,存在很大挑战,令人望而却步。由此,在这些系统中,SiC技术相对于硅IGBT的优势被削弱。

SiC超结的解决方案十分受人关注。该架构打破了单极传导限制,并在中压级应用中提供了特定导通电阻和阻断电压之间的改进权衡方案。

到目前为止,该器件已经进行了几次演示。其中包括跨度为1.2-3.3 kV的多外延SiC超结器件,器件采用了多外延方法。制造此类器件并不容易,因为使用传统工艺设备在SiC中注入原子的抛射深度较浅,因此需要多次进行外延再生长。另一种方法是制作沟槽再填充SiC超结器件。然而,尽管该器件可以处理6.5kV的电压,但由于复杂的再填充过程产生的晶体缺陷,器件在高阻断电压下会出现过度泄漏。

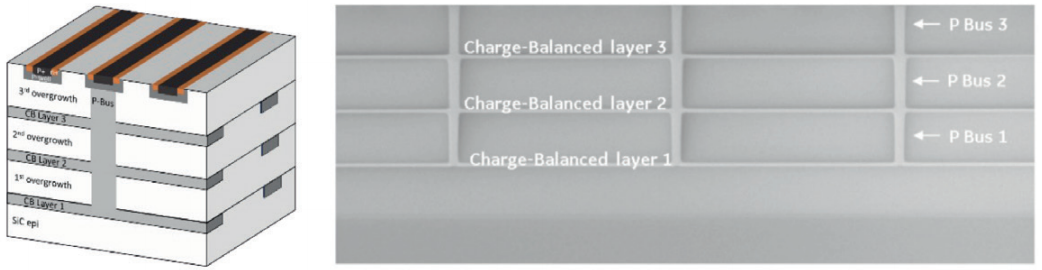

GE Research目前正在探索全新的第三种制造架构,用于生产基于超高能离子注入和外延生长的3.3kV以上的器件。在ARPA-E(ARPA-E DE-AR0000674“用于突破性功率转换的SiC电荷平衡FET”计划)资助的近期已完成项目中,凭借GE Research在SiC电荷平衡器件制造方面的领先能力,研发出了这项技术。在该计划中,我们研发出超结中间体电荷平衡技术(superjunction intermediate charge-balanced technology)。该技术涉及到应用一种全新的漂移层架构,用来创建埋入式电荷平衡p型区域,这些区域通过兆电子伏特高能注入区域,电气性连接到顶部接触区(表示为P-Bus,如图1所示)。与超结柱的情况一样,如果电荷平衡区域设计有最佳注入的p型剂量和间距,可以在阻断期间耗尽周围区域电荷并充当电场分配器。关键的是,对于给定的击穿电压,可以使用比传统设计掺杂更高的漂移层,从而在正向导通模式下实现更低的导通电阻,并消除传统作为击穿电压函数的特定导通电阻的一维极限。

△ 图1. GE的4.5kV SiC电荷平衡MOSFET的示意图(左)和扫描电子显微镜横截面图(右)。这类开关实现了与超结器件类似的外延再生长和高能离子注入。

△ 图1. GE的4.5kV SiC电荷平衡MOSFET的示意图(左)和扫描电子显微镜横截面图(右)。这类开关实现了与超结器件类似的外延再生长和高能离子注入。

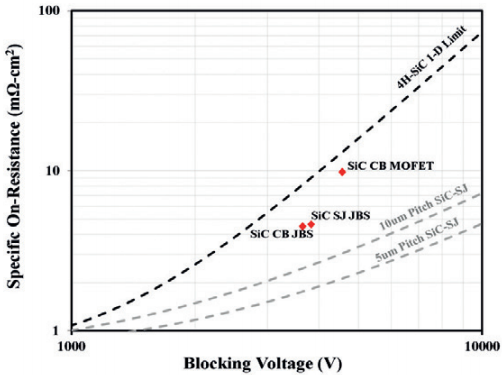

利用上述方法,我们首先生产出性能与20µm节距SiC超结相当的器件,并且其明显优于最先进的高压SiC方法。该研究的最新亮点包括电荷平衡MOSFET的首次实验演示,其微分比导通电阻为10 mΩ cm2,阻断电压超过4.5kV。该比导通电阻值低于作为阻断电压函数的一维比导通电阻,并且比所报道的传统4.5kV SiC FET的值大约低20%。据我们所知,这是迄今为止所展示的所有SiC电荷平衡器件的最高击穿电压,也是所有报道的4.5kV级MOSFET的最低通态损耗。

虽然这一成功十分震撼,但我们知道这只是一个开始。该器件有个缺点是,其用于电荷平衡的堆叠性质以及切换期间所需的电荷载流子会重新分布,存在切换延迟,并且随着每层增加而增加。当SiC电荷平衡器件扩展到4.5kV以上时,这类延迟令人望而却步。

在ARPA(ARPA-E DE-AR0001007“具有超低导通电阻的高级中压SiC-SJ FET”)进一步资助的支持下,目前我们在最初的研究基础上,将电荷平衡架构扩展到全超结器件。我们的最新研究涉及基于深注入柱的全超结器件的制造,该器件是为电荷平衡器件而开发的,用来克服电荷平衡载流子分布延迟所带来的限制。

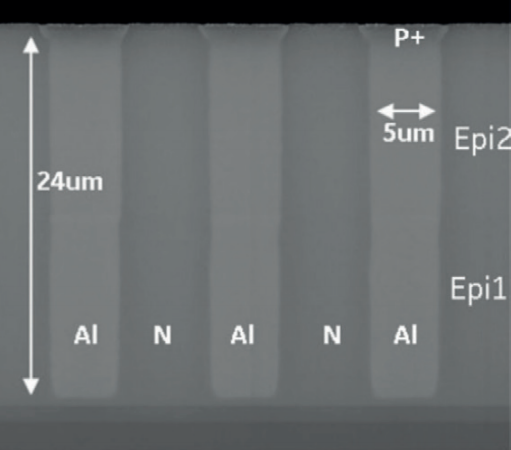

我们的团队开辟了全新领域,展示了世界上首个3.5kV SiC超结深注入型结势垒肖特基(JBS)二极管(见图2)。

△ 图2. 通过两轮外延生长和超高能离子注入,GE Research制造的世界上首个3.5kV深注入型SiC超结结势垒肖特基(JBS)二极管。

△ 图2. 通过两轮外延生长和超高能离子注入,GE Research制造的世界上首个3.5kV深注入型SiC超结结势垒肖特基(JBS)二极管。

该类器件是SiC的重要里程碑,将为我们开发3.3kV SiC SJ MOSFET奠定基础。

我们生产的深注入型超结二极管是利用两轮外延生长(每轮12µm)形成的,产生的总漂移层厚度为24µm。p掺杂和n掺杂柱是使用两轮高能离子注入(MeV)创建的,最大结深为12µm。

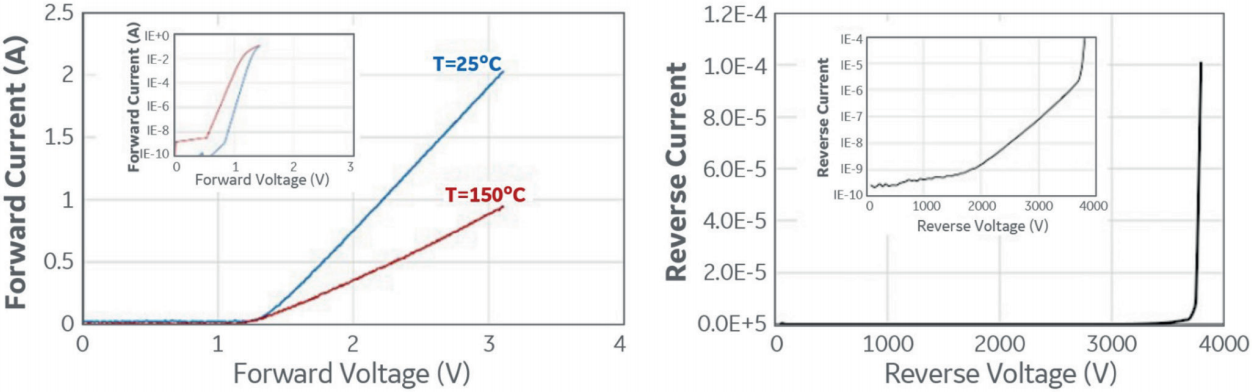

我们还测量了超结JBS二极管的正向和反向电流-电压特性(见图3)。该器件在1.4V时开启,并且在室温下具有4.5 mΩ cm2的特定导通电阻,在150℃时其电阻为9.6 mΩ cm2,这比SiC单极限大约低45%。特定导通电阻是指在一定条件下的导通电阻。此外,其击穿电压为3.8kV。我们观察到击穿前存在较低的漏电流,这表明高能离子注入、外延生长和2000℃的激活退火之后缺陷很小。

△ 图3. 3.5kV深注入型SiC超结结势垒肖特基(SJ JBS)二极管的正向和反向电流-电压(I-V)特性。比导通电阻Ron,sp为4.5 mΩcm2(比SiC单极极限低45%)。

△ 图3. 3.5kV深注入型SiC超结结势垒肖特基(SJ JBS)二极管的正向和反向电流-电压(I-V)特性。比导通电阻Ron,sp为4.5 mΩcm2(比SiC单极极限低45%)。

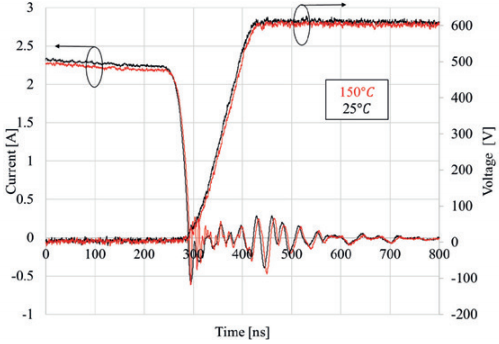

利用AGVA Technologies的ITC57300/57220(见图4),我们对SiC超结二极管进行了反向恢复测量。当结温从常温升高到150℃时,我们没有观察到关断电流和电压波形有任何变化。预计总电容电荷低于700 nC/cm2。

△ 图4. 3.5kV SiC深注入型超结结势垒肖特基(SJ JBS)二极管在室温和150℃下的反向恢复特性。

△ 图4. 3.5kV SiC深注入型超结结势垒肖特基(SJ JBS)二极管在室温和150℃下的反向恢复特性。

通过电荷平衡和超结器件与4H-SiC单极器件和超结极限进行基准测试,证明了我们这两种技术的有效性(见图5)。这两种技术是制造超结器件的多外延和沟槽填充方法的有效替代方案,还为实现中压级高频固态开关提供了可扩展的解决方案。

△ 图5. GE报告的电荷平衡和深注入型超结器件之间的比较,以及4H-SiC单极和超结极限。

△ 图5. GE报告的电荷平衡和深注入型超结器件之间的比较,以及4H-SiC单极和超结极限。

-

本文提供的信息、数据或研究部分由美国能源部能源高级研究计划局(ARPA-E)资助,奖励编号为DEAR0000674和DEAR0001007,由项目总监Isik Kizilyalli提供咨询。本文作者表达的观点和意见不完全代表或反映美国政府或其任何机构的观点和意见。

扩展阅读

-

“IGBT and Diode chips from ABB Switzerland Ltd, semiconductors.” Available at www.abb.com

-

A. Bolotnikov et al. 2015 IEEE Appl. Power Electron. Conf. Expo., pp. 2445–2452.

-

L. Han et al. “A Review of SiC IGBT: Models, Fabrications, characteristics, and Applications” IEEE Trans. Power Electron. 36 2080 (2021)

-

T. Tanaka et al “First Demonstration of Dynamic characteristics for SiC Superjunction MOSFET Realized using Multi-epitaxial Growth Method,” 2018 IEEE Int. Electron Devices Meet., p. 8.2.1-8.2.4, 2019.

-

M. Baba et al. “Ultra-Low Specific on-Resistance Achieved in 3.3 kV-Class SiC Superjunction MOSFET,” 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2021, pp. 83-86

-

R. Kosugi et al “Breaking the Theoretical Limit of 6.5 kVClass 4H-SiC Super-Junction (SJ) MOSFETs by Trench-Filling Epitaxial Growth,” in 2019 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2019, pp. 39-42.

-

P. Thieberger et al. “Novel high-energy ion implantation facility using a 15 MV Tandem Van de Graaff accelerator,” Nucl. Instruments Methods Phys. Res. Sect. B Beam Interact. with Mater. Atoms 442 36 (2019)

-

R. Ghandi et al. 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Sep. 2020, pp. 126–129.

-

Z. Chen et al. “Effect of Annealing Conditions on Recovery of Lattice Damage in a High-Energy-Implanted 4HSiC Superjunction PIN Diode,” ECS Journal of Solid State Science and Technology 11 065003 (2022)

| 上一篇:多维功率器件 | 下一篇:一种削减成本的合理方法... |