如何整合硅和III-V族

2025/1/6 16:06:41 材料来源:ACT化合物半导体

为了利用规模化带来的所有传统优势,必须在硅代工厂通过外延和制程将硅和 III-V 族集成起来

为了利用规模化带来的所有传统优势,必须在硅代工厂通过外延和制程将硅和 III-V 族集成起来

作者:Eugene Fitzgerald、Fayyaz Singaporewala、Daniel Lepkowski和Johanne Chu,New Silicon 公司

主流半导体行业正继续朝着同一方向发展。一如既往,重点是硅晶体管的微型化。如今,这方面的成功使更多的晶体管可以集成在IC上,从而使芯片的功能更加强大。这种方法提高了内存和算力,但随着该行业的不断成熟,预计将迎来商业化的不断进深。

除了扩大规模以外,硅产业还在探索其他方向。这包括硅与化合物半导体的结合,这种结合前景广阔,因为它提供了两全其美的机会。化合物拥有卓越的性能,比如,强大的光发射、高阻断电压以及射频领域的效率和功率;硅产业具备低成本、高产量和令人印象深刻的工具集 ;将硅产业和化合物相结合的前景十分诱人。

至关重要的是,当化合物与硅结合在一起时,后者的相关技术优势能够得以保留。高密度器件、通过扩展提高性能和降低成本的需求占据了这一价值清单的首位。

从历史上看,器件密度的提高一直是微处理器、多核处理器和硅存储器改进的主要推动力。未来,可容纳数百万像素的增强现实显示器、像素化光源和高效单芯片相控阵列都需要高晶体管和LED密度。

总体而言,微型化在提高“性能”的同时降低了“成本”。微型化可以提高电路频率、降低功耗、减少寄生、降低噪音和散热性能。据预测,微型化带来的这些性能提升优势将持续下去,并可能为LED和HEMT等高密度器件阵列的数字控制带来新的发展空间。

规模化带来的成本削减不仅是由于单位面积内电路数量的增加,从而确保了每个电路生产成本的降低。还需要考虑器件之间互连的平均成本——这取决于互连的长度,较短的互连更具成本效益。

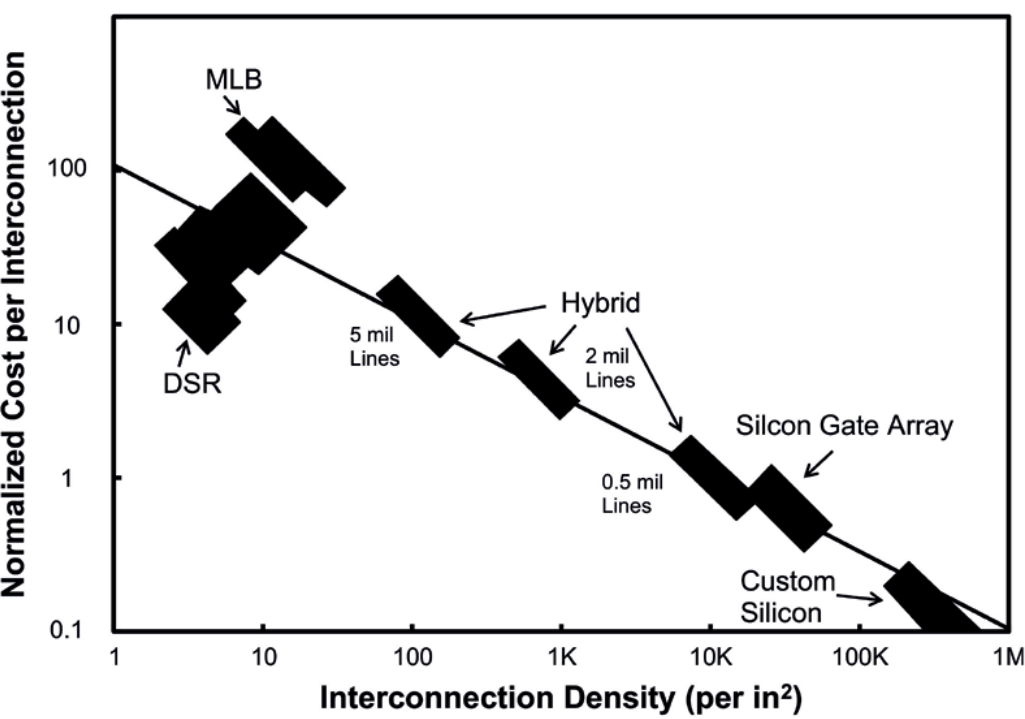

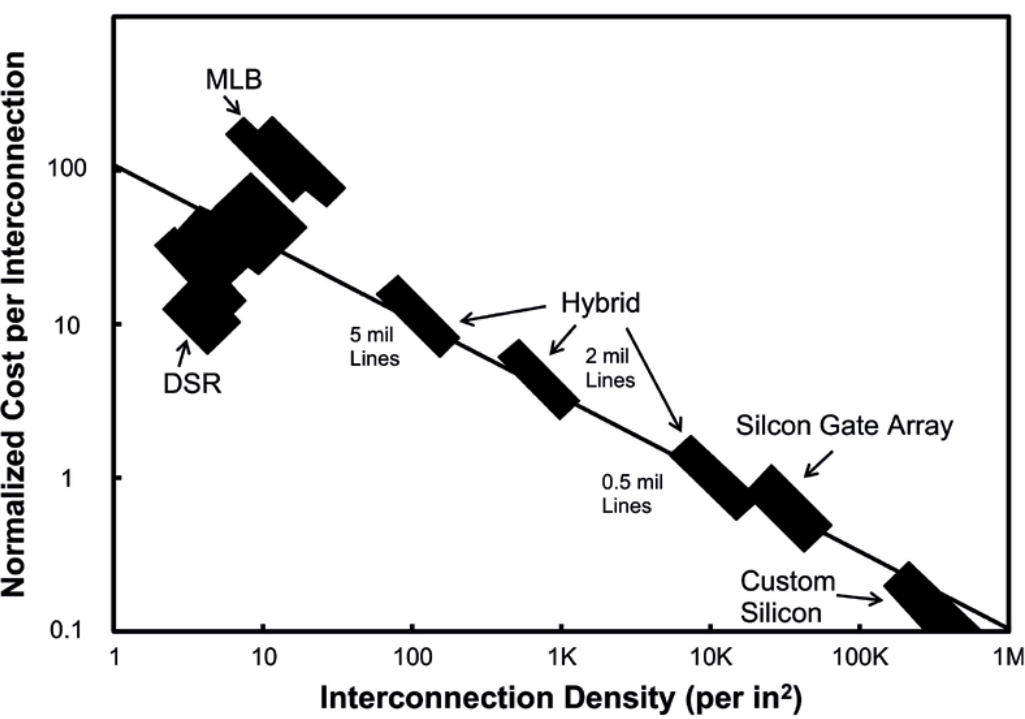

自20世纪80年代以来,人们已经了解了芯片级单片集成的经济学原理。(图1展示了互连密度、单位互连成本和器件密度之间的关系)。自1984年以来,我们取得了长足的进步。当时互连密度低于每平方英寸10,000个,在电路板/封装级而非芯片级实现互连具有经济意义。在这几年中,芯片中引入了越来越多的布线层,互连也从板级或封装级迁移到了芯片级。

△ 图1:单位互连成本与互连密度的关系。定制硅和硅栅阵列是单片硅芯片(CMOS的BEOL是高密度晶体管的互连)。1984年,当芯片级的互连密度(以及器件密度)降低到每平方英寸约10,000个互连点时,成本有利于在电路板/封装级制造更长的互连点。[改编自W.H. Knausenberger和L.W. Schaper,"Interconnection Costs of Various Substrates - The Myth of Cheap Wire",IEEE Transactions on Components, Hybrids, and Manufacturing Technology,CHMT-7卷,第261-263页,1984年9月。]

△ 图1:单位互连成本与互连密度的关系。定制硅和硅栅阵列是单片硅芯片(CMOS的BEOL是高密度晶体管的互连)。1984年,当芯片级的互连密度(以及器件密度)降低到每平方英寸约10,000个互连点时,成本有利于在电路板/封装级制造更长的互连点。[改编自W.H. Knausenberger和L.W. Schaper,"Interconnection Costs of Various Substrates - The Myth of Cheap Wire",IEEE Transactions on Components, Hybrids, and Manufacturing Technology,CHMT-7卷,第261-263页,1984年9月。]

除了刚才概述的三个优势——新型芯片的可能性、更高性能和降低成本——还有其他与硅制造相关的优势,在采用化合物半导体时也应保留。这些优点包括高产量、高可靠性和快速的产品设计周期。由于在多种产品中使用相同的制造工艺,产量和可靠性得到了稳步提高。此外,用于在线和后道测量的低成本自诊断能力也有助于实现高产量,这些都是集成设计流程所带来的便利。

另一项优势是采用了通用的硅晶圆制造工艺,从而提高了通过该工艺的产品数量,并推动了产量、可靠性和成本效益的提高。最重要的是,尽管采用了通用方法,但每个客户都保留了自己的设计知识产权。

与LED集成

一个极具吸引力的集成机会是通过使用数百万个晶体管来驱动和处理数百万个LED像素,从而形成单芯片LED显示屏。在这种情况下,这些显示器中的LED密度与早期微处理器中的晶体管密度相当。因此,与这些微处理器的情况一样,将所有这些元件封装在一起的意义不大,因为要达到这样的密度是不可行的,成本太高,而且这种方法会抵消单片集成在产量和可靠性方面的优势。

我们可以将一系列产品(包括可穿戴设备、虚拟现实和增强现实)中的LED密度与历史上的晶体管密度进行比较(见图2)。该图显示,当LED成为硅制造的一部分,并利用CMOS后道制程(BEOL)方法与CMOS相互连接时,LED显示屏的制造可能会被打乱。请注意,反对这种趋势的观点是荒谬的,这就像认为奔腾处理器应该通过大规模转移或拾取贴装技术等方法将单个晶体管封装在一起一样毫无意义。

△ 图2:图中的线代表了晶体管密度随时间推移的历史性增长。叠加的是当前和未来LED显示屏产品的LED密度。随着CMOS + GaN LED的单片硅集成电路制造技术的发展,微型显示器将采用单芯片,并在硅晶圆厂生产。

△ 图2:图中的线代表了晶体管密度随时间推移的历史性增长。叠加的是当前和未来LED显示屏产品的LED密度。随着CMOS + GaN LED的单片硅集成电路制造技术的发展,微型显示器将采用单芯片,并在硅晶圆厂生产。

为了支持单芯片显示器的发展,我们在新加坡的New Silicon Corporation公司团队已经开发出必要的材料、工艺、结构、器件和软件设计模块,以及利用硅集成电路制造技术制造出可以将CMOS器件和氮化镓基LED结合在一起的集成电路。我们的首批产品将是白色或单色LED,后者有红色、绿色和蓝色可选。对于红色和绿色的变体,发射将来自由泵浦量子点的蓝光产生。今后,我们计划生产集成的全彩显示屏,在红色和绿色像素上使用量子点。

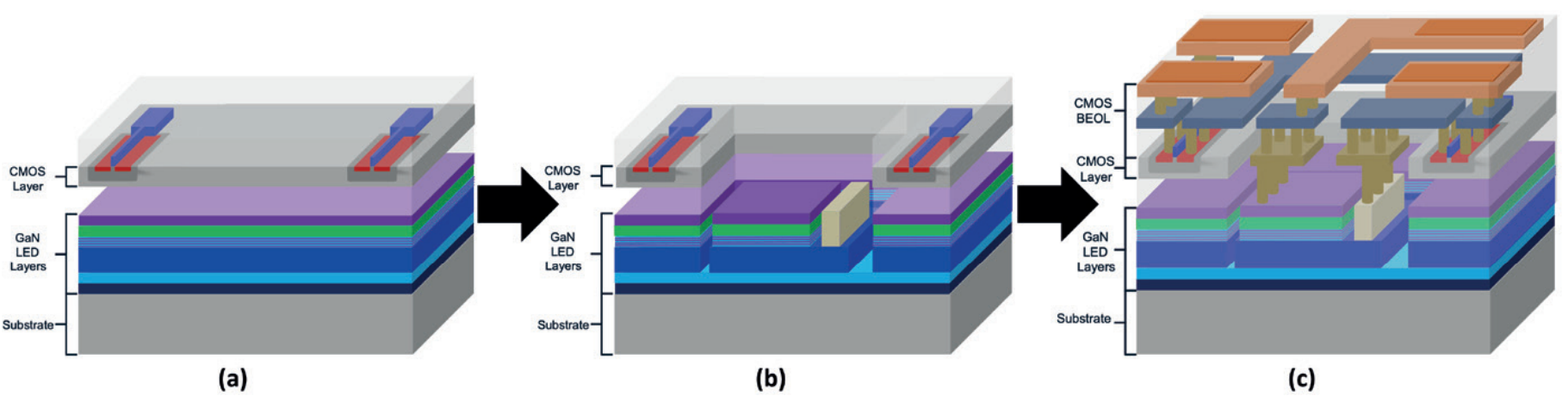

我们的CMOS + III-V工艺包括三个阶段(见图3):CMOS前道工序(FEOL)、新的III-V FEOL和CMOS BEOL。第一个和最后一个阶段直接采用标准硅CMOS制造工艺,该工艺通过在硅晶片上使用FEOL工艺,利用在BEOL中形成的多层金属互连网络连接晶体管,从而生产出完整的电路。在我们的CMOS + GaN LED工艺中,我们将GaN FEOL夹在CMOS FEOL和BEOL之间。GaN LED制作完成后,BEOL的互连网络将CMOS晶体管和LED连接起来,形成一个单片集成电路。硅CMOS BEOL可作为硅和III-V器件的互连网络。这种方法可以利用标准集成电路设计软件实现集成设计环境。

△ 图3:创建CMOS + III-V电路的单片工艺首先是在硅晶体管加工完成后,在与硅晶体管相同的晶圆上加工III-V器件。硅工艺的顺序掩膜策略(每个掩膜都与前一个掩膜对齐)对于处理平台在众多产品领域获得集成和微型化优势至关重要。(a)根据设计在代工厂制作标准硅FEOL,然后转移到硅基III-V外延片上。(b)III-V族器件FEOL制作完成,通过顺序掩膜自动与硅FEOL对齐。(c)顺序掩模形成硅BEOL,根据电路设计将硅晶体管和III-V族器件互连起来。图表未按比例或适当长宽比绘制。

△ 图3:创建CMOS + III-V电路的单片工艺首先是在硅晶体管加工完成后,在与硅晶体管相同的晶圆上加工III-V器件。硅工艺的顺序掩膜策略(每个掩膜都与前一个掩膜对齐)对于处理平台在众多产品领域获得集成和微型化优势至关重要。(a)根据设计在代工厂制作标准硅FEOL,然后转移到硅基III-V外延片上。(b)III-V族器件FEOL制作完成,通过顺序掩膜自动与硅FEOL对齐。(c)顺序掩模形成硅BEOL,根据电路设计将硅晶体管和III-V族器件互连起来。图表未按比例或适当长宽比绘制。

采用硅前道和后道工艺生产III-V族器件的一个巨大优势在于,每个掩膜都与前一个掩膜对齐,从而保证了整个晶片的产量和可靠性。此外,这种方法还消除了分别制造硅晶体管和III-V器件,然后试图使用晶圆级金属键合和对齐来实现器件互连时出现的问题。当III-V器件位于单独的晶圆上时,要在两种具有不同材料堆叠和热膨胀系数的晶圆上实现高密度对齐是个问题,而且良率很低,尤其是在200毫米或更大的晶圆尺寸上。

将III-V族元素和硅结合在一起的另一个挑战是,优化两个器件层的可用晶圆面积。当采用晶圆键合来组合硅芯片和III-V族芯片时,III-V族器件所占的面积与硅电路所占的面积不同。因此,晶圆上未使用的区域——通常是III-V晶圆——需要用来铺展电路元件,以便与晶圆上的其他芯片对齐。这种做法远非最佳,因为它降低了单位面积的有效芯片数,增加了成本。可惜的是,这一基本的成本和设计限制往往被忽视,有限的案例和随之而来的更高成本阻碍了潜在的晶圆销售量,进一步提高了晶圆键合方法的单片晶圆成本。

更好的方法是真正的单片集成。与硅集成电路设计和制造一样,我们使用顺序掩膜,将硅和III-V器件混合在一起进行集成电路设计。无论是电路还是芯片,这种方法都能实现最紧凑的面积和最高效的设计。由于所有设计都采用相同的工艺,因此晶圆体积最大化,有助于确保最低的单位晶圆成本。

我们的单片工艺的一个关键步骤是将CMOS FEOL转移到硅基GaN外延片上。转移后,CMOS FEOL仍留在外延片表面,类似于普通的CMOS外延片。CMOS FEOL表面下的GaN LED磊晶被隐藏起来,但通过蚀刻承载CMOS FEOL的顶部薄硅表面,仍可在特定区域加工GaN LED。

利用我们的方法,为LED制造预留的区域必须与CMOS元件分开。这可以通过将III-V器件模型纳入标准CMOS设计工具包来实现,该工具包由提供FEOL和BEOL服务的代工厂提供。工艺设计套件(PDK)的开发对于弥合集成电路设计与芯片制造半导体代工厂之间的差距至关重要。

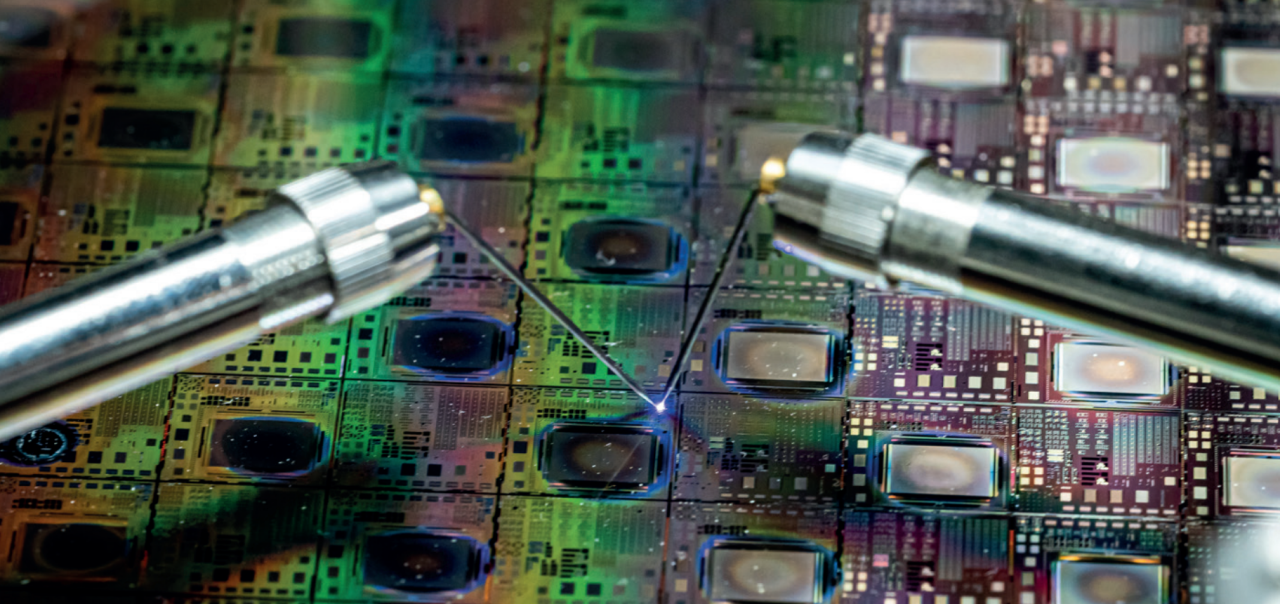

我们开发了集成CMOS + GaN PDK,为大规模电路仿真、设计和布局验证提供全面的解决方案。该PDK允许在我们专有的集成CMOS + GaN晶圆技术上进行电路设计和制造。我们的PDK库专为CMOS + GaN产品量身定制,可满足传统CMOS或GaN代工厂产品组合范围之外的独特应用。得益于工艺开发和集成电路设计团队之间的密切合作,我们对每个方面都进行了精心的微调,从而确保在集成电路设计和制造之间架起一座稳健可靠的桥梁。我们努力推动显示器、照明和无线系统芯片解决方案进入一个新时代,并克服硅基III-V集成电路设计和制造所面临的挑战(图4为已加工的200 mm CMOS + GaN LED电路示例)。

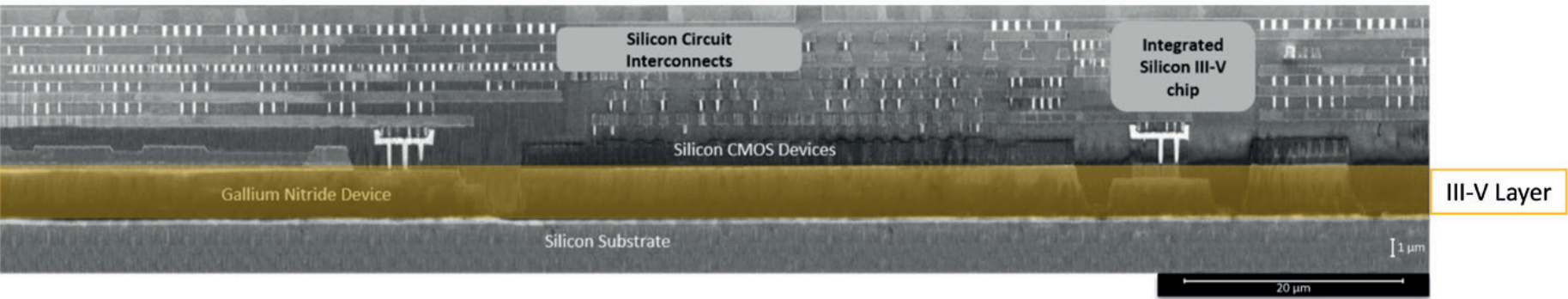

△ 图4:采用硅代工制造工艺加工的200mm成品晶圆的透射电子显微镜截面图。用于BEOL的钨插头工艺也用于连接III-V FEOL。

△ 图4:采用硅代工制造工艺加工的200mm成品晶圆的透射电子显微镜截面图。用于BEOL的钨插头工艺也用于连接III-V FEOL。

迄今为止,我们一直专注于推出我们的初始平台,即CMOS + GaN LED平台。不过,我们的单片集成电路工艺可应用于任何CMOS + X平台,其中X可以是III-V族或其他半导体材料或器件。要实现集成,必须具备以下条件 :有能力在硅片上生产外延器件层,其直径要适合硅产线制造;这些外延器件层的缺陷密度要足够低,以确保电路中的最终集成器件在整个产品生命周期内保持令人满意的性能。

随着数字控制功率放大器产量的增加,我们正准备推出下一个产品:用于5G/6G的单芯片相控阵。更快的数据传输速率导致无线通信频率的增加,但其弊端是大气吸收率更高。因此,需要将高频无线信号的传输集中到手机接收站。在过去的基础设施中,这可以通过移动碟形天线来实现。然而,这在消费类设备中并不可行。在智能手机等设备中,将无线波束以电子方式转向接收器的一种方法是使用一个芯片,芯片中装有多个GaN HEMT,它们在平面上以特定的距离精确排列。我们认为,这些单芯片相控阵能以较低的成本在硅工厂制造,对于扩大高带宽消费无线系统的部署至关重要。

毫无疑问,III-V族材料和器件与硅集成电路的整合,为硅产业开辟了全新的细分市场。对于硅产业来说,在集成电路微型化、集成化和规模化的推动下,新器件与硅系统的单片集成将决定下一阶段的增长。这将创造新的高增长市场,以极具竞争力的成本生产高性能系统。

我们目前的重点是miro LED照明和显示市场。根据Spherical Insights和Straits Research的分析,该市场在2022年的价值为6.5亿美元,预计到2030年将以超过80%的复合年增长率攀升,届时价值将达到365亿美元。消费电子设备(包括高端智能手机和头戴式设备等可穿戴显示器)对更明亮、更强大的显示面板的需求推动了这一市场的发展。

| 上一篇:微射流激光切割GaN晶体... | 下一篇:双势垒阳极结构实现0.3... |